HBM IP核使用

HBM知识的扫盲以及IP核的使用。

HBM简介

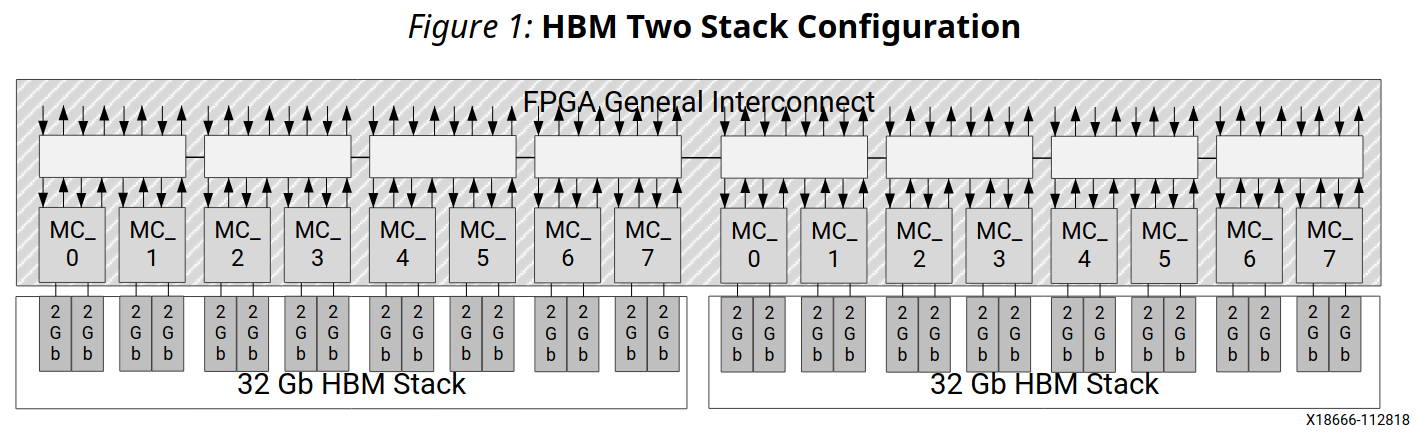

HBM分为2个stack,每个stack有8channel,每个channel可以分为2个伪通道(pseudo channel),那么就一共有32个pseudo channel。

|

可以认为HBM是32个堆叠的DDR,每个DDR应用AXI3总线协议,使用起来和控制DDR也非常相似。

IP核配置

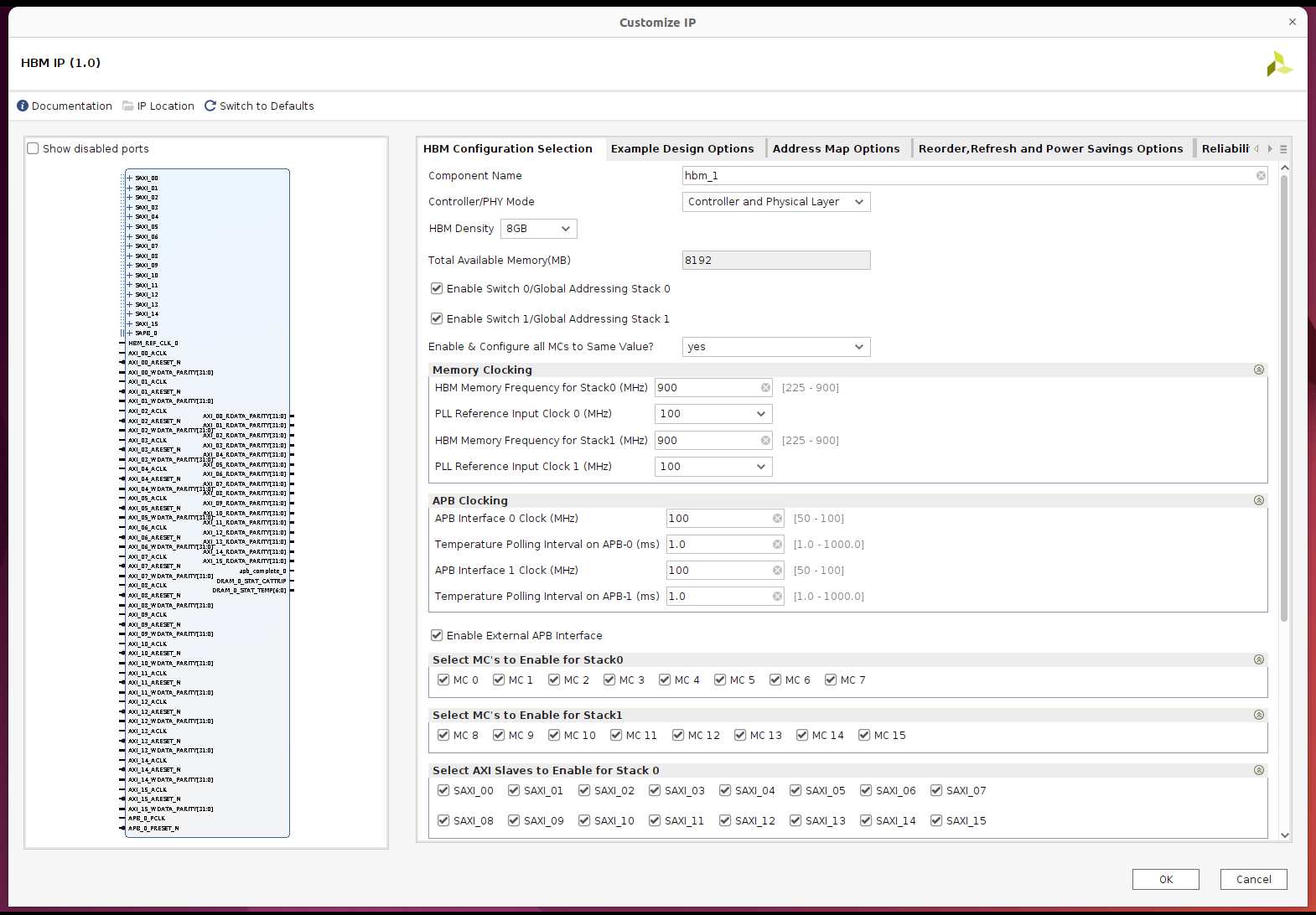

Configuration

|

- Component Name: 组件名称作为模块生成输出文件的基名称。姓名必须以字母开头,必须由字符组成:a到z,0到9,和’ _ ‘。

- Controller/PHY Mode: 在一个完整的控制器和物理层选项之间进行选择,或者只选择一个物理层设计。

(这里我们不自己设计控制器,因此保持默认) - HBM Density:选择1或2个内存堆栈进行配置。在选定存储密度后,相应地更新下面的Total Available Memory字段。MC Stack子选项卡中的设置也会影响显示的内存值。

- Stack Select: 选择单个堆栈配置的物理位置( LEFT / RIGHT )。在选定了堆栈的物理位置后,在IP XDC中对LOC约束进行了相应的修改。

(这里由于同时选择了两个stack,所以这里未出现该选项) - Total Available Memory (MB):显示了基于HBM密度以及启用的内存通道数的总可用内存。

- Enable Switch (0/1)/Global Addressing Stack (0/1): 勾选该选项以实现全局寻址。选择这个选项允许以延迟为代价的全局寻址的灵活性。如果禁用,则每个AXI端口只能访问分配给它的伪信道。

- 全局寻址:是一种内存访问方式,它允许系统中的多个 AXI 端口 访问相同的全局内存空间。也就是说,所有的端口可以使用统一的地址映射来访问内存,而不再局限于每个端口只能访问固定的内存区域。

- 伪通道(Pseudo Channel):在不启用全局寻址时,系统通常会将每个 AXI 端口 限制为只能访问 特定的伪通道。伪通道是内存的一个逻辑划分,不同的 AXI 端口只能访问它们各自的伪通道。

- Enable and Configure all MCs to Same Value: 选择Yes将所有内存通道设置为相同的值。GUI引用中的所有选项MC0和所有MC0设置都应用于所有已启用的内存通道。为该选项选择No显示了每个内存通道的选项。

(该选项主要影响Address Map Option选项卡,具体在相应章节讨论。) - Enable External APB Interface: 使外部APB接口能够写入/读取记录的控制器状态和性能寄存器。

- HBM Frequency for Stack 0/1 (MHz): 指定存储器接口时钟( ck _ t )频率。向导在内部生成必要的PLL设置以生成此内存时钟频率。

(此时钟由 PLL(相位锁定环) 生成,具体的频率设置是通过 PLL Reference Input Clock 来控制的) - PLL Reference Input Clock (MHz): 规定了核心用于产生HBM时钟的PLL参考时钟频率。

- APB Interface 0/1 Clock (MHz): 规定了寄存器接口( APB )的时钟频率。该频率应与APB _ PCLK _ *端口驱动的精确频率相匹配。

- Temperature Polling Interval on APB-0/1 (ms): 指定温度传感器内部读取并在DRAM _ x _ STATE _ TEMP端口输出的时间间隔。间隔以毫秒为单位指定。

- Select MCs to Enable for Stack 0/1:MC Stack的标签列表中列出了每个栈中所有的内存通道控制器,每个控制器可以单独启用或禁用以节省功耗。

- Select AXI Slaves to Enable for Stack 0/1:AXI Slaves部分根据Global Address选项和已启用的MC列出了堆栈中可使用的所有可能的AXI端口。

- Switch Clock Select 0/1:为AXI Switch选择使用的时钟。IP自动默认为一个大致位于启用的内存通道中间的时钟。每个存储器通道有2个AXI端口可用。如果存储器通道0,2,3和7被启用,这意味着AXI端口0,1 (对于MC0 ),4,5 (对于MC2 ),6,7 (对于MC3 ),14和15 (对于MC7 )被启用,并且可以选择用于开关时钟。

(此选项用于选择 AXI Switch 使用的时钟。AXI Switch 是一个交换机制,用于在多个 AXI 端口 之间路由数据。) - Select Line Rate for Each MC of Stack 0/1:选择了存储器通道的工作频率。该设置根据IP配置自动更新,仅供参考。

(MC 控制器的频率)

Example Design

下图为HBM IP的”示例设计选项”选项卡。

|

这一部分不多赘述。

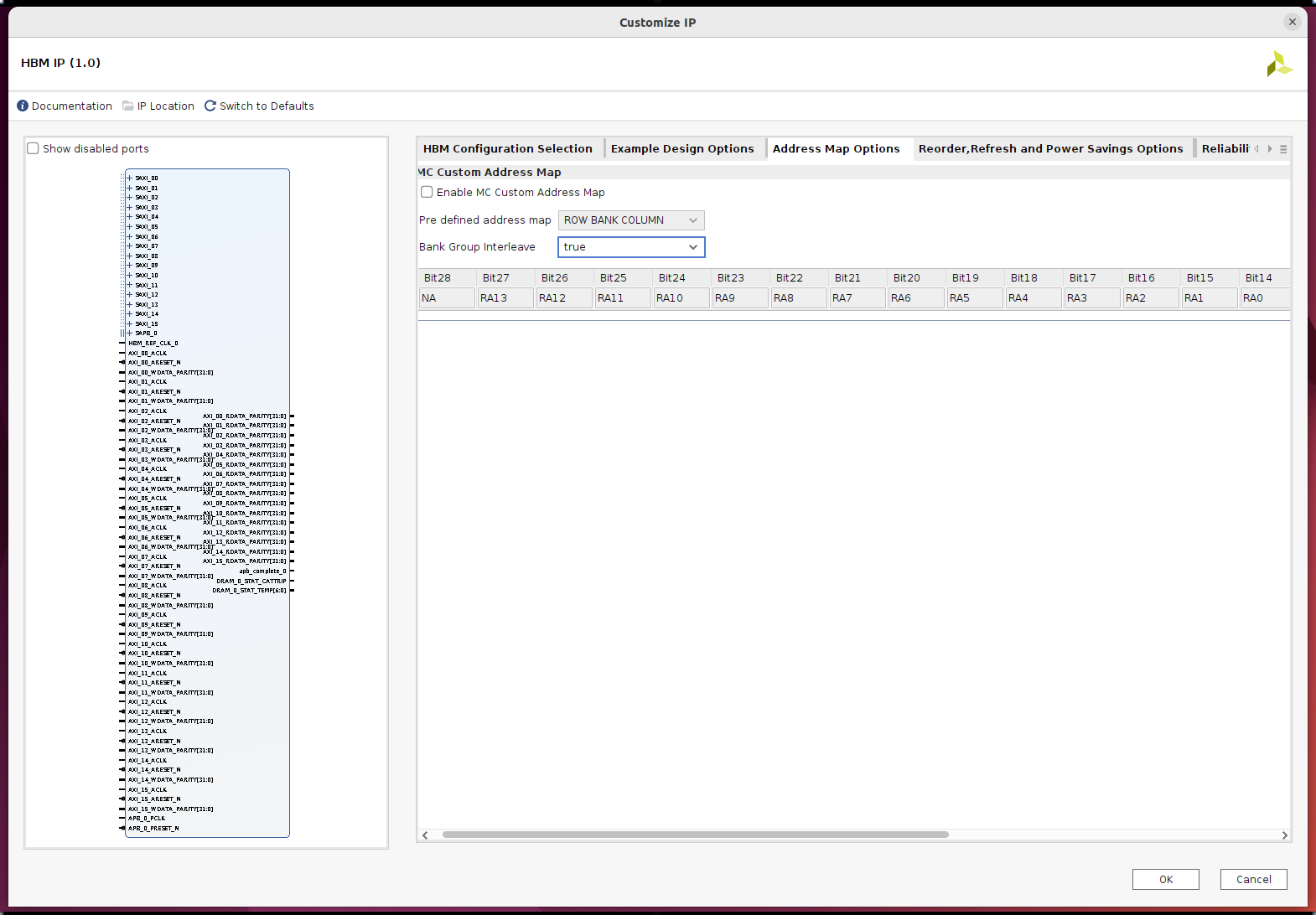

Address Map

|

Custom Address Map: 如果默认设置不理想,则检查自定义地址映射框。可以定义从AXI地址到HBM地址的映射。如果没有检查,则分配默认设置。如果在Configuration选项卡上设置Configure MCs to the Same Value选项,则只显示MC0,并将所有MC设置为该值。如果该选项不被设置,那么所有启用的MC都会出现。选择Custom Address Map与”Reordering”选项卡中的所有”re-ordering”选项不兼容。

8Gb内存空间需要33位进行寻址(AXI Addressing):

区分stack 区分伪通道 真正地址 数据位宽 十进制 2个 16个 8Gb 32 Byte 位宽 1 4 23 5 Bit[4:0]为无用比特位,原因是数据位宽为256bit,每次都要最少传输256bit,那么就需要32Byte对齐,所以其低5bit永远为0。

综上,8Gb的内存,需要28位进行控制。Physical Address Map映射:

1

2

3

4

5

6

7

8

9HBM Stack

└─ Channel (pseudo-channel)

└─ Bank Group (BG)

└─ Bank (BA)

└─ Row (RA)

└─ Column (CA)

AXI 地址位 : [27 ............ 14][13][12:11][10:6][5]

逻辑信号名称: RA[13:0] BG1 BA[1:0] CA[5:1] BG0

功能含义 : 行地址 bank组1 bank号 列地址 bank组0

Bank Group Interleave: 使顺序地址操作能够在偶数组和奇数组之间交替进行,以最大限度地提高内存效率。随机访问模式可能无法从这种设置中获益。

Reoder,Refresh and Power Savings

|

- Select Traffic Pattern: 流量模式可以选择为Linear、Random或User _ Defined。对于线性和随机流量模式,向导配置IP为给定的流量模式提供最优性能。当选择User _ Defined流量模式时,没有提供预定义的配置。

- Reorder Options

(注:这些选项仅在不使用custom address map的情况下可用。)- Enable Request Reordering: 这使得控制器可以在64个深度窗口内重新排序命令,以提高效率。这种重新排序与AXI3接口中基于ID标签的重新排序不同。

- Coherency in Reordering: 允许控制器重新订购命令,前提是它们不在同一行和行中。

(允许对命令重排序,但是前提是不在同一bank和Row。) - Reorder Queue Age Limit: 设置了在待处理的AXI命令之前可以发布的更新的AXI命令的最大数量。这允许调整任何AXI命令的最大延迟,而不是重新排序以获得最佳的内存吞吐量。

(Enable Request Reordering 是大分组,Reorder Queue Age Limit是大分组里的小分组,在小分组里重拍) - Enable Close Page Reorder: 当启用时,这会在指令完成后关闭一个页面。当禁用时,该页面保持打开状态,直到同一银行的另一个页面请求更高的优先级操作。

- Enable Lookahead Pre-Charge, Activate: 这些用于允许控制器通过优化12个命令队列中的命令来最大限度地提高吞吐量。如果这些选项被禁用,所有命令都按照收到的命令进行处理。

(内存读取步骤:预充电->激活->读取/写入) - Enable Lookahead Single Bank Refresh: 这使得控制器可以根据待处理操作插入刷新操作,以实现效率的最大化。直到启用”单一银行刷新”选项,该选项才具有可选择性。

(内存需要定期刷新,自动周期刷新,对内存访问性能有影响) - Minimum Period to issue Subsequent Single Bank Refresh: 为单个银行刷新的最小周期输入一个值。

(频繁刷新没必要,也存在一定副作用) - Disable Dynamic Open Page:当检查时,动态打开页模式被禁用,纯打开页模式被启用。

(动态页面:动态决定页面的打开和关闭,会有自动的机制调控;纯打开界面:打开了就不关闭,直到其他高优先级的操作需要访问其他行才关闭。)

- Refresh Options

- Single Bank Refresh:银行被单独刷新。这会影响银行访问顺序,以最小化所需的刷新次数。

- Enable Refresh Period Temperature Compensation: 控制器根据内存stack的温度调节刷新率。

- Hold Off Refresh for Read/Write: 该选项允许延迟刷新以允许读写操作完成。为了补偿这种延迟,可能需要更频繁地刷新。

- Power Saving Options

- Idle Time to enter Self Refresh Mode: 在这几个空闲周期之后,控制器将所有的内存行列放置在自刷新中。当配置为’ 0 ‘时,该功能被禁用。

- Idle Time to enter Power Down Mode: 在这几个空闲周期之后,控制器将所有的内存行列都放在掉电模式下。当配置为’ 0 ‘时,该功能被禁用。控制器仍然按照期望的刷新间隔生成刷新命令。

(自刷新模式允许某些其他操作,低功耗模式则几乎只允许刷新命令存在。两者都降低了功耗,但后者功耗更低,恢复到正常模式的延迟更长。) - Enable Temperature Controlled Self-Refresh Intervals: 在自刷新时,根据内存温度,根据需要调整刷新率。这只适用于”Idle Time to enter Self Refresh Mode”具有非零值的情况。

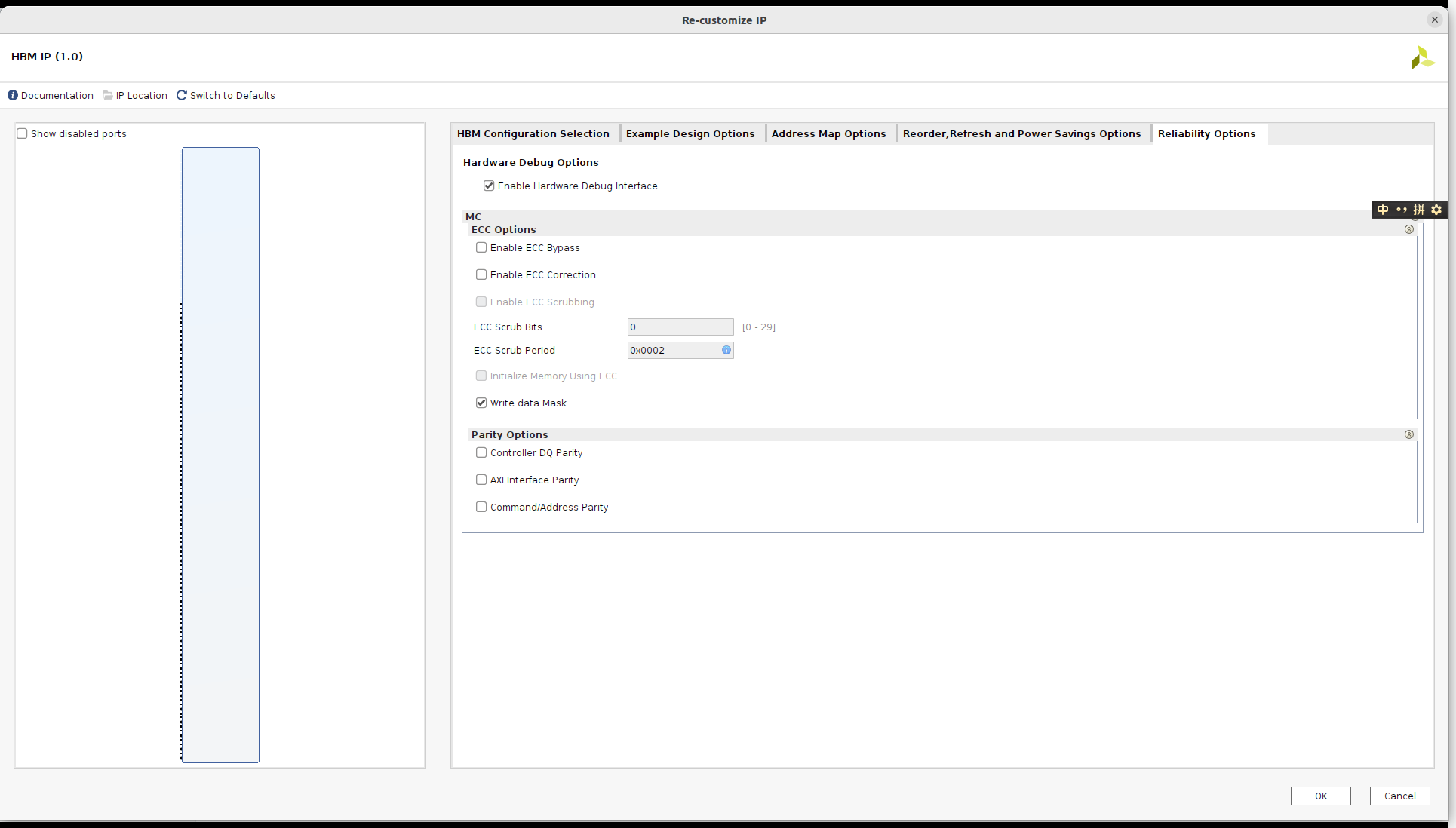

Reliability

|

Enable Hardware Debug Interface: 使HBM IP中的XSDB硬件调试器内核能够在Vivado硬件管理器中看到HBM的属性和状态。

Enable ECC Bypass: 启用时,控制器不计算ECC校验数据,也不对接收数据进行ECC校正。在ECC旁路模式下,wdata _arity输入引脚被重定向为写入ECC内存的数据。同样地,rdata _arity输出被重定向为从ECC内存中读出的数据。

当启用ECC旁路时,写数据掩码( Write Data Mask )功能自动禁用,小事务执行读修改写操作。Enable ECC Correction: 当选取时,纠正单比特错误,只检测双比特错误。在这两种情况下,这些值都被记录在状态寄存器中。

Enable ECC Scrubbing: 该选项要求启用 ECC Correction。这样可以实现对存储器的连续刷新,纠正单比特错误。

ECC Scrub Bits: 用于ECC初始化和擦写的内存地址位数。如果设置为0,则使用当前配置的内存的默认最大位数。

(可以控制ECC操作涉及的内存地址范围,适用于一些特殊需求)ECC Scrub Period: ECC擦洗读操作间隔时间。该值以256个存储器时钟周期为单位。例如,取值为2意味着每次读取之间的延迟为2x256 = 512个内存控制器时钟周期。

Initialize Memory Using ECC: 该选项要求启用ECC校正。这样就用有效的ECC值初始化了全存储阵列。

Write Data Mask: 该选项与ECC Correction或ECC Bypass不兼容。这使得使用写数据掩码的能力成为可能。

Controller DQ Parity: 实现了Controller Dq(数据总线)奇偶校验的写入和读取。这是由HBM控制器根据JEDEC规范生成的。当选中这个选项时,重试也被启用。

AXI Interface Parity: 启用顶层AXI Write / Read数据校验端口,并设置用户必须随着Write载荷突发而提供Write校验数据的期望。当启用时,如果Write DQ奇偶校验与有效载荷不匹配,则会出现BRESP SLVERR。用户应用程序必须将读取的DQ奇偶校验数据与响应载荷进行比对,以防出错。奇偶校验按每8位数据计算。因此,对于256位的数据总线,有32位的奇偶校验端口。

Command/Address Parity: 启用奇偶校验位用于命令和地址。

端口解析

DRAM_STAT

- DRAM_y_STAT_CATTRIP: Hbm灾变温度标志。当DRAM的温度超过120℃时,断定为该位。当该位被断言时,确保立即禁用内存访问。

- DRAM_y_STAT_TEMP: [ 6:0 ]摄氏度。这是两个内存堆栈的最坏情况。当两个存储器堆栈的温度超过5 ° C时,在DRAM _ y _ STAT _ TEMP的两个端口上都驱动出了两者的最高温度。当两个存储器堆栈的温度低于5℃时,两个堆栈的最低温度在DRAM _ y _ STAT _ TEMP端口上都被驱动出来。更新频率是可配置的。当两个Stack启用的设计的IP中有两个端口时,由于是由单个源驱动的,所以两个端口上的数据是相同的。

- apb_complete_y: 表明Stack - y的初始配置序列完成。

APB

- APB_y_PCLK

- APB_y_PENABLE

- APB_y_PRESET_N: 低电平复位。当该位被断言时,它将重置整个内存接口,包括控制器、PHY和内存堆栈。运行在APB _ PCLK域中,可以异步断言/断言,最小脉冲宽度为一个APB时钟周期。

- APB_y_PSEL

- APB_y_PWRITE

- APB_y_PADDR

- APB_y_PWDATA

- APB_y_PRDATA

- APB_y_PREADY

- APB_y_PSLVERR

AXI3

在AXI_xx_ARADDR和AXI_xx_AWADDR信号中:

- 使用4H Stack Bit [ 32 ],8H Stack [ 33 ]来选择HBM Stack。

- 使用4H Stack Bits [ 31:28 ],8H Stack [ 32:29 ]来选择AXI端口。

- 4H Stack Bits [ 27:5 ],8H Stack [ 28:5 ]用于访问实际的HBM。

- 由于AXI _ xx _ ARSIZE和AXI _ _ xx _ AWSIZE信号始终为3 ‘ b101 ( 32字节对齐),因此未使用比特[ 4:0 ]。

Clocking

- HBM_REF_CLK_x: HBM _ REF _ CLK _ x驱动PLL,PLL产生8个存储控制器的时钟,以及HBM堆栈的存储时钟。每个HBM堆栈有一个PLL。这个时钟必须来自一个MMCM / BUFG,或者来自一个BUFG。HBM _ REF _ CLK _ x可以从另一个时钟衍生的级联时钟源中获得。该衍生时钟的源时钟必须来自与HBM相同的SLR内的GCIO引脚。驱动GCIO的时钟发生器抖动应小于3 pS RMS。

- APB_x_PCLK: APB _ x _ PCLK用于APB寄存器端口的访问。这可以与其他时钟异步。每个HBM堆栈有一个APB时钟端口。APB _ x _ PCLK可由级联时钟源或MMCM或GCIO引脚产生。

- AXI_xx_ACLK: AXI _ xx _ ACLK是每个AXI端口的时钟。这些时钟可以与其他时钟异步。AXI _ xx _ ACLK可以从级联时钟源或MMCM或GCIO引脚获得。